# Lecture Notes

# for

# **Combinational Logic Circuits**

### (PHYS4008: Electronics)

### Dr. Pawan Kumar

(Assistant Professor) Department of Physics Mahatma Gandhi Central University Motihari-845401, Bihar

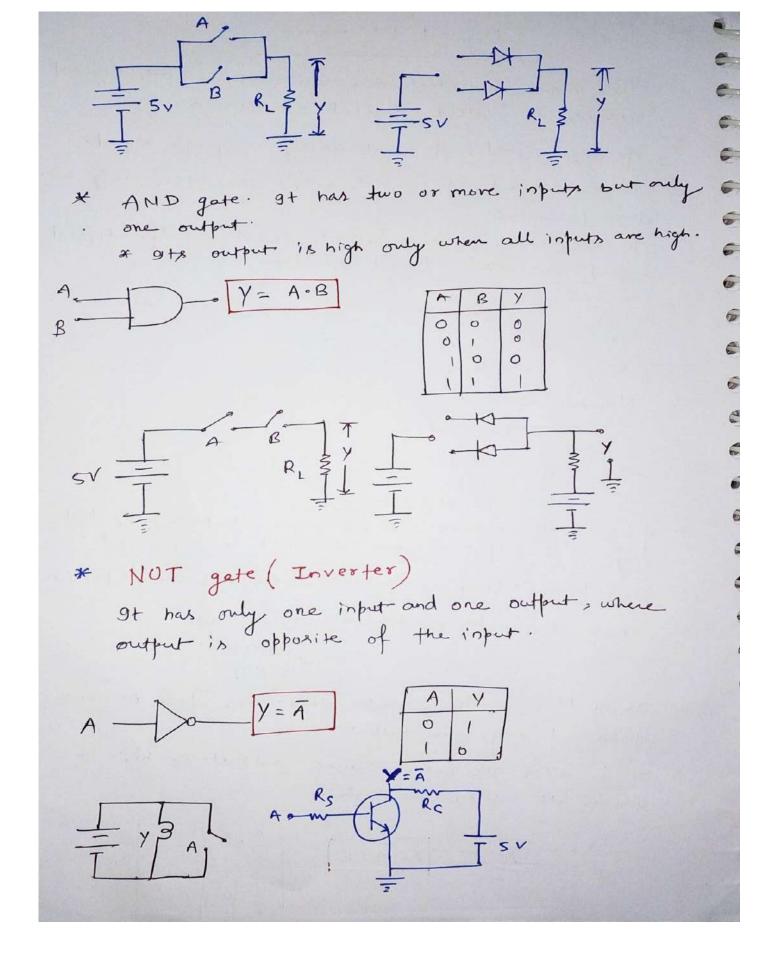

Digital Electronics \* The branch of electronics which deals with digital circuity is called digital electronics. \* Analog signal : A continuourly varying signal. Digital signal: A signal which can have only two \* discrete values. \* An electronic circuit which handles only digital signal is called digital circuity. logic system tre logic -re logic Number Systems × 1. Decimal 2. Binary 3. Octal 4. Heradecimal \* Adigital circuit with one or more input signals but only one output signal is called a logic gate. \* The term " lugic" refers to decision making process. Three basic logic gates are i) OR gate > AND " in NOT " \* OR gate : A logic gate that has two or more inputs but only one output .. It is called OR gate because output is high if any or all inputs are high. B Y= A+B A A = y = A + B0 0 0

Combination of Basic logic device 1. NAND gate !  $\begin{array}{c} A \\ B \end{array} \end{array} \begin{array}{c} A \\ B \end{array} \begin{array}{c} A \\ B \end{array} \end{array} \begin{array}{c} A \\ B \end{array} \begin{array}{c} A \\ B \end{array} \end{array} \begin{array}{c} A \\ B \end{array} \begin{array}{c} A \\ B \end{array} \begin{array}{c} A \\ B \end{array} \end{array} \begin{array}{c} A \\ B \end{array} \begin{array}{c} A \\ B \end{array} \begin{array}{c} A \\ B \end{array} \end{array} \begin{array}{c} A \\ B \end{array} \end{array} \begin{array}{c} A \\ B \end{array} \begin{array}{c} A \\ B \end{array} \begin{array}{c} A \\ B \end{array} \end{array}$  \end{array} S 3 The output from NAND gate is always I except 0 when all of the inputs are 1. 3 2. NOR gate :  $\begin{array}{c} A \\ B \end{array} \end{array} \xrightarrow{A+B} \xrightarrow{Y=A+B} = A \xrightarrow{Y=A+B} \\ B \xrightarrow{Y=A+B} = B \xrightarrow{Y=A+B} \end{array}$ > The output from a NOR gate is I only when 3 all inputs are D. 3. Exclusive OR gate (Y = A @B) Y=AB+AB  $y = \frac{1}{2}$ Y A B-0 0 0 0 4. Exclusive NOR gate. Y = AB + AB 1 1 1 (XNOR)  $y = \overline{A} \oplus B = A \odot B$ y B  $Y = \overline{A \oplus B} = A \oplus B$ 0 0 6 0 0 0

| De Morgan's theorem.                                |

|-----------------------------------------------------|

| $* \overline{A + B} = \overline{A \cdot B}$         |

| $\frac{*}{A \cdot B} = \overline{A} + \overline{B}$ |

| * A+AB = A                                          |

| * 1+B=1=1+A                                         |

| * AA = 0                                            |

| $A(\overline{A}+B) = AB$                            |

| * A+A = 1                                           |

| * NAND, and NOR gate acts as universal              |

| gate because either NAND or NOR gate                |

| Can be combined to make all baric gates.            |

\* Decimal to Binary

...

| 23 + 2 | 4 | 11 | ; | remain | der | = | 1 |   |

|--------|---|----|---|--------|-----|---|---|---|

| 11 ÷ 2 | 1 | 5  | 5 | 17     |     |   |   |   |

| 5+2    | " | 2  | ; | 'n     | 13  |   |   |   |

| 2÷2    | = | 1  | ; | 17     | **  |   |   |   |

| 1+2    | 1 | 0  | ; | 1.     | ۰,  | - | Т | 1 |

$$(23) = (0111)_{0}$$

Approx result of 0.55 is  $(0.55)_{10} = (0.100011)_{2}$

>>When there is I carry in the last position of the result of addition in step (b), the cavory is removed and added to the scrult without the carry to obtain the final answer. ⇒ If there is no I carry in the last place, the result is -ve and is in its is complement. \* Binary substraction by d'& complement. The d's complement of the number to be substracted is added to the number from which the substraction is desired and the carry in the last place is rejected. \* The I carry in the last position of the result In a's complement method implies that answer 18 +ve. \* The absence of a 1 caroup in the last position indicates that the answer of substraction is -ve and is in 2's complement. \* Octal Number System : 97 has a base of 8.  $879 \div 8 = 109$ ; remainder = 7 109 + 8 = 13 ; 7 = 5 13 - 8 = 1 ; " - 5 1 - 8 = 0 ; " = 1 (879) = (1557)8 \* Hexadecimal Number system: It uses a base of 16. 980:16 = 61; remainder = 4 61 - 16 = 3 ; " = 13  $3 \div 16 = 0;$  m = 3 (980) = (304) 16

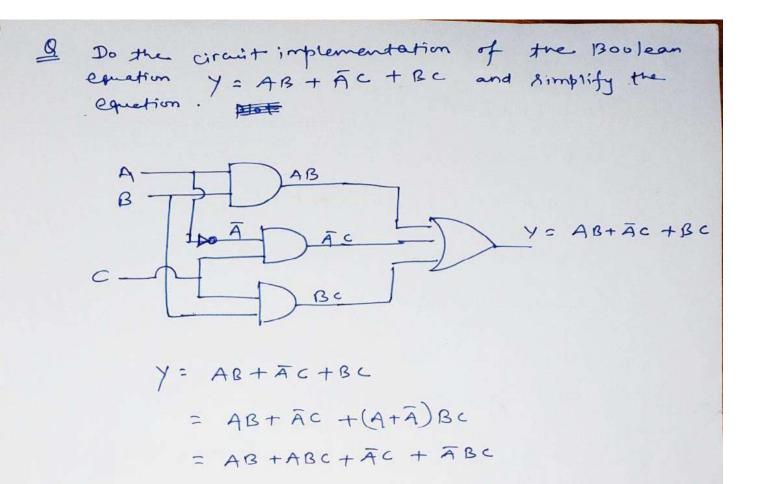

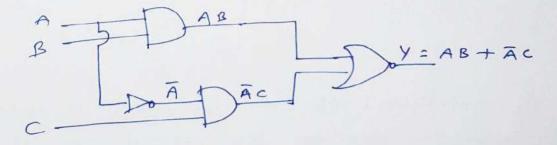

= AB + AC

= AB(1+c) + Ac(1+B)

\*  $A + \overline{A}B = (A + AB) + \overline{A}B$ =  $(AA + AB) + \overline{A}B$ =  $(AA + AB) + \overline{A}B$ =  $AA + AB + \overline{A}A + \overline{A}B$ =  $(A + \overline{A}) (A + B)$ =  $A + B + \overline{A}A$

D

D

Simplify

$$(a.b.(c+bd) + a.b) \cdot c.d$$

$= (a.b.(c+bd) + a.b.(a+bb) \cdot c.d$

$= a.b.(c+a.b.b+a.b(a+bb) \cdot c.d$

$= (a.b.c+a.b.d+b+b) \cdot c.d$

$= (a.b.c+d+a.b.d+b+b) \cdot c.d$

$= (a.b+a.b) \cdot c.d$

$= (a.b+a.b) \cdot c.d$

$= c.d Are$

Sol:  $(321)_8 = 201$   $3 \cdot 2 \cdot 1$

$\int_{011}^{3} \int_{010}^{3} \int_{000}^{3} \int_{000}^{3} \int_{000}^{3} \int_{0}^{3} \int_{000}^{3} \int_$

\* (A+B)(A+C)= AA + AC + AB + BC = A + AC + AB + BC = A(1+C) + AB + BC= AL + AB + BC = A(1+B) + Bc= A.L+BC = A+BC ANY  $\star (\bar{A} + B)(A + B) = \bar{A}A + \bar{A}B + AB + BB$ = AB+AB+BB = (A+A+1)B = B Any \*  $\left(\overline{AB}\left((+BD)+\overline{AB}\right)c\right)$ = (ABC + ABBD+AB)C = (ABC + AB) C = ABCC + ABC = ABC + ABC = (A+A)BC = Bc Am \*  $(\chi+\gamma) \left[\overline{\chi}(\overline{\chi}+\overline{z})\right] + \chi\overline{\chi} + \chi\overline{z}$  $(x+y)\left[\overline{x}+(\overline{y}+\overline{z})\right]+\overline{x}\overline{y}+\overline{z}\overline{z}$  $(x+y)(x+\overline{y},\overline{z})+\overline{x}\overline{y}+\overline{x}\overline{z}$  $xx + xyz + xy + yyz + \overline{xy} + \overline{xz}$  (:: xz = x) x (1+y+yz) + yz + xy + zz x+ Yz+ xy+ xz (:: 1+y+yz=1)  $(x+\overline{z}\overline{y})+yz+\overline{z}\overline{z}=(x+\overline{z}\overline{z})+(\overline{y}+\overline{y}z)=(x+\overline{z})+(\overline{y}+z)$  $x+\overline{y}+yz+\overline{z}\overline{z}=x+\overline{y}+1=x+\overline{y}$  Any.

1

0

ed ed ed

3

3

3

.

2

3

3

>

5

2

-5

-

-

3

eg. ABC + AB + ABED (non-standard sup from) . 1  $A\overline{B}C(D+\overline{D}) + \overline{A}B(C+\overline{E})(D+\overline{D}) + AB\overline{C}D$ 0 = ABCD + ABCD + (ABC + ABE) (D+D) + ABED 1 = AB(D+AB(D+ AB(D+AB(D+ABCD+ABCD+ 0 2 ABZD = Standard SOP form. 2 i) Product of Sum (pos) form : A sum term 0 (also called a max-term) is the sum of literals D (or Buolean variables). In logic circuit, a sum term is produced by an OR operation only. 2 \* when two or more sum terms are multiplied, 0 the resulting expression is POS -3 Identify the non-standard sum terms in the given \* 2 expression. To each non-standard sum term, add a product term consisting of a mixing variable and its complement. & convert the Buolean expression (A+B) (B+c) to a standard product of sum form.  $(A+\overline{B})(B+c) = (A+\overline{B}+c\overline{c})(B+c+A\overline{A})$ =  $(A + \overline{B} + c) (A + \overline{B} + \overline{c}) (A + B + c) (\overline{A} + B + c)$ of the output is o for binary value 000,001 Q 100, and 101.  $(000 \rightarrow A+B+c$  $\begin{array}{c} 601 \xrightarrow{\rightarrow} A + B + \overline{c} \\ 100 \xrightarrow{\rightarrow} \overline{A} + B + c \end{array}$ 101 - A+B+C The resulting standard pos expressions for the output  $X = (A+B+c) (A+B+\overline{c}) (\overline{A}+B+c) (\overline{A}+B+\overline{c}) A_{ms}$

3

5

5

5

3

B The remaining combinations of variables (freevious Quart

for which output is I are 010, 011, 110, and 111.

$$\therefore 010 \rightarrow \overline{ABC}$$

$011 \rightarrow \overline{ABC}$

$110 \rightarrow ABC$

$110 \rightarrow ABC$

$110 \rightarrow ABC$

The remaining SOB expression for the output X is

$X = \overline{ABC} + \overline{ABC} + \overline{ABC} + \overline{ABC}$

The truth fable for above two quartions.

$X = \overline{ABC} + \overline{ABC} + \overline{ABC} + \overline{ABC}$

$X = \overline{ABC} + \overline{ABC} + \overline{ABC} + \overline{ABC}$

$X = \overline{ABC} + \overline{ABC} + \overline{ABC} + \overline{ABC}$

$X = \overline{ABC} + \overline{ABC} + \overline{ABC} + \overline{ABC}$

$X = \overline{ABC} + \overline{ABC} + \overline{ABC} + \overline{ABC}$

$X = \overline{ABC} + \overline{ABC} + \overline{ABC} + \overline{ABC}$

$X = \overline{ABC} + \overline{ABC} + \overline{ABC} + \overline{ABC}$

$X = \overline{ABC} + \overline{ABC} + \overline{ABC} + \overline{ABC}$

$X = \overline{ABC} + \overline{ABC} + \overline{ABC} + \overline{ABC}$

$X = \overline{ABC} + \overline{ABC} + \overline{ABC} + \overline{ABC}$

$X = \overline{ABC} + \overline{ABC} + \overline{ABC} + \overline{ABC}$

$\overline{ABC} + \overline{ABC} + \overline{ABC} + \overline{ABC} + \overline{ABC}$

$\overline{ABC} + \overline{ABC} + \overline{ABC} + \overline{ABC} + \overline{ABC}$

$\overline{ABC} + \overline{ABC} + \overline{ABC} + \overline{ABC} + \overline{ABC}$

$\overline{ABC} + \overline{ABC} + \overline{ABC} + \overline{ABC} + \overline{ABC}$

$\overline{ABC} + \overline{ABC} + \overline{ABC} + \overline{ABC} + \overline{ABC}$

$\overline{ABC} + \overline{ABC} + \overline{ABC} + \overline{ABC} + \overline{ABC}$

$\overline{ABC} + \overline{ABC} + \overline{ABC} + \overline{ABC} + \overline{ABC}$

$\overline{ABC} + \overline{ABC} + \overline{ABC} + \overline{ABC} + \overline{ABC}$

$\overline{ABC} + \overline{ABC} + \overline{ABC} + \overline{ABC} + \overline{ABC}$

$\overline{ABC} + \overline{ABC} + \overline{ABC} + \overline{ABC} + \overline{ABC}$

$\overline{ABC} + \overline{ABC} + \overline{ABC} + \overline{ABC} + \overline{ABC} + \overline{ABC}$

$\overline{ABC} + \overline{ABC} + \overline{ABC} + \overline{ABC} + \overline{ABC} + \overline{ABC}$

$\overline{ABC} + \overline{ABC} + \overline{ABC} + \overline{ABC} + \overline{ABC} + \overline{ABC}$

$\overline{ABC} + \overline{ABC} + \overline{ABC} + \overline{ABC} + \overline{ABC} + \overline{ABC} + \overline{ABC}$

$\overline{ABC} + \overline{ABC} + \overline{A$

Construct a forth table for the standard g sop expression ABC + ABC + ABC Boin: we note that there are 3 variables in the

domain; so there are eight possible compinations of binary values. The binary values that make the product terms in the expression equal to 1 are 001 for ABC, 100 for ABC and 111 for ABC. For each of these binary values, a 1 is placed in the output column. For each of the remaining binary combinations, a 0 is placed in the output column.

| A   | B   | Les and the second s |

|-----|-----|-----------------------------------------------------------------------------------------------------------------|

| 0   | 0   | > 0                                                                                                             |

| ٥   | 0   |                                                                                                                 |

| 0   | 1 0 | 0                                                                                                               |

| 0   | 1 1 | 0                                                                                                               |

| L 🥵 | 0 0 |                                                                                                                 |

| 1   | 0 1 | 0                                                                                                               |

| 1   | 1 0 | 0                                                                                                               |

| 1   | 1 1 | 1                                                                                                               |

.

)

.)

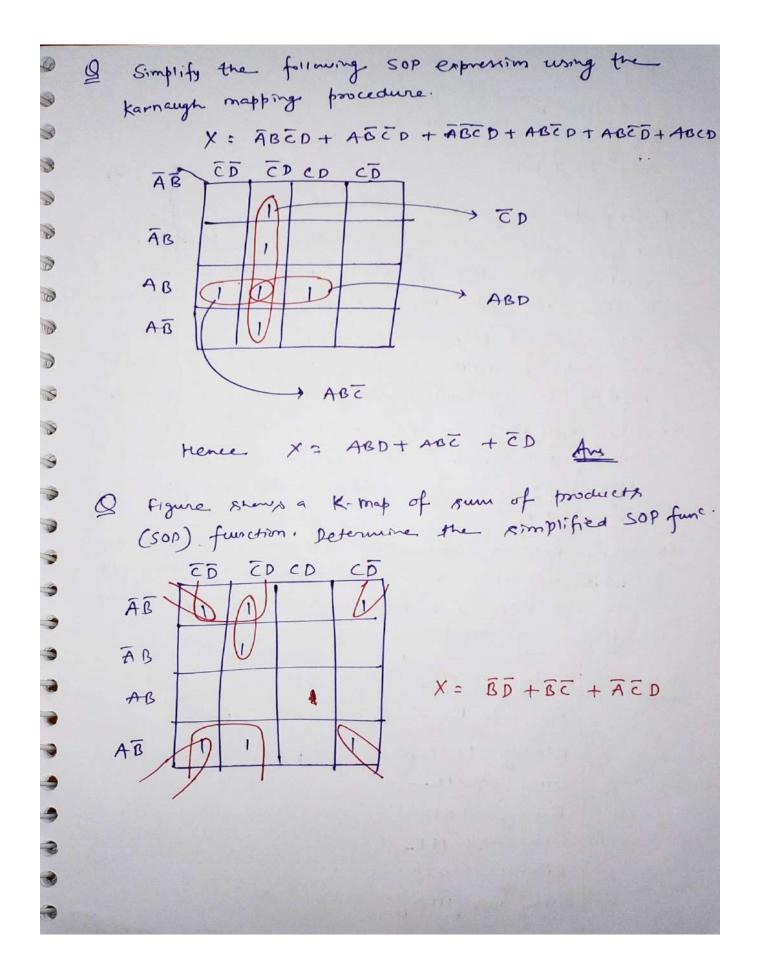

## KARNAUGH MAP (K-map)

This is graphical technique which provides a system. - atic method for simplifying and manipulating Boolean 6 expressions. In this technique, the information e contained in a touth table or available in pus or 1 SOP form is represented on Karnaugh map (K-map). \* Although the technique may be used for any number of variables, it is generally used up to -Bix variables beyond which it becomes very cumbersome 6 \* In an n-veriable. K-map, there are 2" cells. 6 Each cell corresponds to one of the combinations 6 of n variables, Since there are 2° combinations of n variables. 5 Two variable Karnaugh map 0 \* Truth table Boolean Expression B y A Y = A.B + AB 6 0 1 0 1 0 0 0 1 of the the the of the the B B K-map A 0 1 0 A 1

Three Variable Karnaugh map y = ABC + ABC + ABC + ABC + (SOP)  $Y = (A+B+c)(A+\overline{B}+\overline{c})(\overline{A}+B+\overline{c})(\overline{A}+B+\overline{c})(\overline{A}+B+c) \leftarrow (POS)$ C 48 00 ~ ~ ~ ~ ~ ~ ~ ~ ~ ~ ~ ~ ~ ~ ~ ~ A B Y C K t --- $Y = \sum m(1, 2, 4, 7)$  $Y = \pi M(0, 3, 5, 6)$

\*\*\* Rules for minimization of SOP from. \* We have 'to prepare the k-map first and look for combination of ones on the K-map. We Mare to combine the ones in much at way that the resulting expression is minimum. The following algorithm can be used which will definitely lead to minimized expression. >1. Identify the ones which cannot be combined with any other ones and encircle them. These are Resential poince implicants. > 2. Identify the ones that can be combined in groups of two, four and eight adjacent ones in only one way. Encircle them in groups 3. After identifying the essential groups of 2.4 and 8 ones, if there still remains some ones which have not been encirculed then there are to be combined with cach other of with other already encircled ones. Any (one) can be included any number of times without affecting expression. Minimizes the four variable lugic function Q. wing K-map f (A, B, C, D) = Em (0, 1, 2, 3, 5, 7, 8, 9, 11, 14) AB 12 00 + (A, B, C, D) 13 DI = ABCD + BC + BD + AD + AB15 1 11 The 1 in cell 14 cannot be combined 14 10 with any other 1. It corresponds to 10 ABCD.

Gray code: 97 was designed by Frank Gray at Bell lobs and potented in 1953. It is unweighted binary code in which two successive value differ only by I bit. Binary to Gray code conversion? L' Begin with most significant bit (MSB) of binory number. The MSB of the Gray code equivalent it the same as the MSB of given binary number 2. The second MSB in the gray code number is Obtained by adding the MSB and the second MSB of binary and ignoring the carry, if any. 3. The third MSB in the carray code number is obtained by adding the second MSB and third MSB is the binary number and ignoring carry, any 十 4. The process continues autill we obtain the LSB of the crays code, number by the addition of the LSB and next higher adjacent bit of the binary number. e.g. Binary 1011 (nray code 1 ----Binary 1011 Gray code 11\_-Bmany 1011 Caray code 111\_ Binary 1011 Gray code 1110

Gray to Binary conversion 2. Begin with MSB. The MSB of binary number is the same as the MSB of the Groay code number. 2. The bit next to MSB (and MSB) in binary number is obtained by adding the MSB in the binary number to the second MSB in the Gray code number and disregarding the carry if any. 3. The 3rd MSB in the binary number is obtained by adding the 2nd MSB in the binary number to third MSB in the Crivary code number. Ignore 4. The process continues untill we obtain LSB of binary number. Gray code 1110 e.g. Binary 1---Group code 1110 Binary 10 --(rray code 1110 Brange 101\_ Gray wede 1110 Binary 1011 I used in Transmission line of degited signals Applications because it minimizes the occurrance of error 2. preferred in angle measuring device. It has also cyclic property suitable for angle 3. used for lebelling of K-map. 4. used to address program memory in computers for power consumption minimization.

ASCII Code : American Standard Code for Information Exchange . It is used to represent the alphaneumeric data in computers, and communication equipments . It was first published as a standard in 1967. It was subsquently updated and published an ANSIX3.4-1968, then as ANSIX3.4-1977 and finally as ANSI X3.4 -1986. \* Since, it is Seven bit code, it can be used to represent 128 characters. \* It currently defines Is pointable characters including 26 upper-case letter (A to Z), 26 lower Cose letters (a to z), 10 numeral (0 to 3) and 33 special characters including methematical symbols, punctuation marks and space characters. \* In addition, st defines codes for 33 nonpointing, mostly obsolete control characters that affect how text is processed. \* An eight bit version of ASCII code, known as USASCII-8 or ASCII-8 has also been developed. of can represente 256 characters.

Logic gate circuits \* It can be divided into two categories based on whether they are with feedback sequential lugic Circuit or without feedback combinational logic circuit. \* Digital electronics is divided into combinational and sequential lugic. \* constructional logic gots output depends on the input levels whereas sequential begic output depends on stored herels of past data and also the present isput levels. \* Combinational Logic : combinational logic & circuit is used to realize different lugic functions using different logic gates. Adder ! grixwed to add two or more bits. \* Half adder : It is a combinational logic circuit, which is used to add two bits and generate output as sum (s) and carry (c). C B S A - Sum S= A@B 0 0 6 0 0 0 1 1 Bon 0 0 Carry C = AB 0 \* Full Adder: gt is used to add three or more bits. The reasons for the name full adden is that it can add the carry bit (Cin) along with other two inputs A and B.  $S = (A \oplus B) \oplus C_{in}$ Cout = Cin (A @ B) + AB

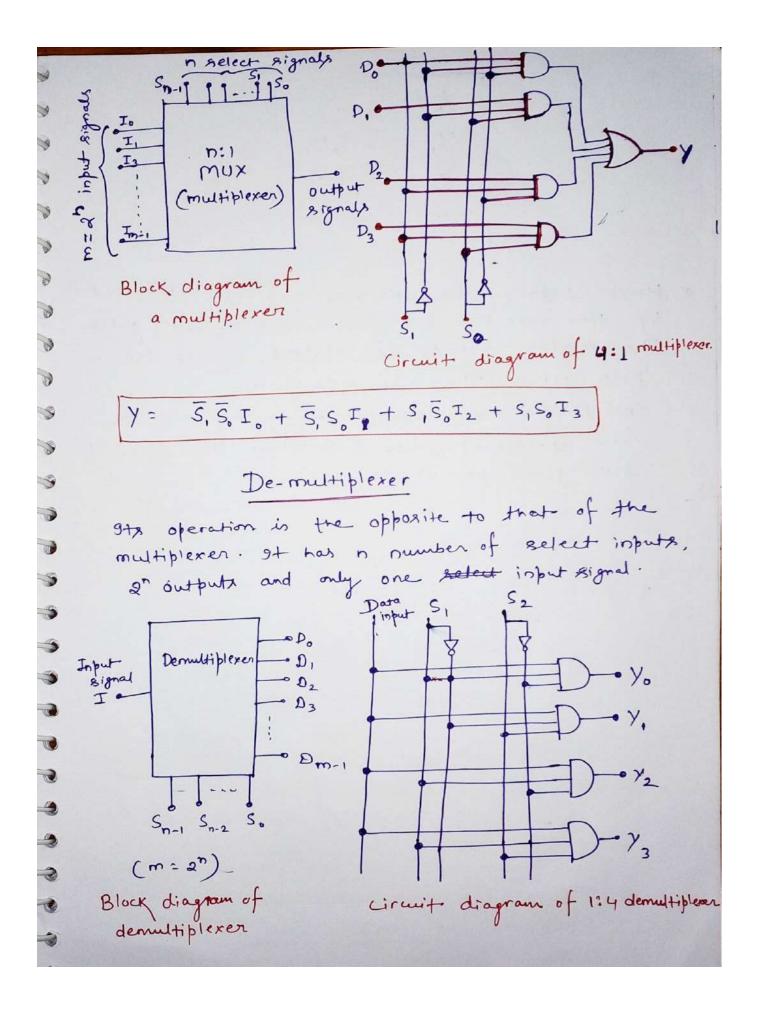

Circuit dragram of full Adder. S Cont output Input Cy Cin B 5 0 0 0 0 D 0 0 0 0 0 0 0 - Touth table of full adder. 1 1 1 0 0 0 0 1 0 1 0 1 0 0 Multiplexer \* It is a special combinational circuit that is one of the most widely used standard circuit in digital design. The multiplexer (or data selector) is a logic × 0 circuit that gates one out of several inputs ~ ~ ~ ~ ~ ~ ~ to single output. \* The relection of input is controlled by a set of relect mputs. \* A multiplexer has n number of select inputs, 2" inputs, and only one output.

$Y_{0} = \overline{S}, \overline{S}_{0} D$   $Y_{1} = \overline{S}, S_{0} D$   $Y_{2} = S, \overline{S}, D$   $Y_{3} = S, S_{0} D$ Hence 1-to-4 demultiplexer can be implemented by two inverters and four 3-input AND gates. The Kingle input D is applied to all the AND gates. The two select line S, & So Enable any me with the Enable any one AND gate at a time and the data appears at the output of the relected AND gate as shown in Figure.

#### **References:**

- 1. Digital Fundamentals by Thomas Floyd

- 2. Digital principles and Applications by A. P. Malvino and D. P. Leach

- 3. Modern Digital Electronics by R.P. Jain

- 4. Digital Design by M. Mano

- 5. Electronics Fundamentals and Applications by D. Chattopadhyay and P.C. Rakshit

- 6. Electronic Devices and Circuits by J. Millman and C.C. Halkias

- 7. Integrated Electronics by J. Millman and C.C. Halkias