#### Lecture Notes for Logic Family

(Electronics : PHYS4008)

Dr. Pawan Kumar Assistant Professor Department of Physics Mahatma Gandhi central university Motihari-845401,Bihar

### **OVERVIEW**

>Introduction

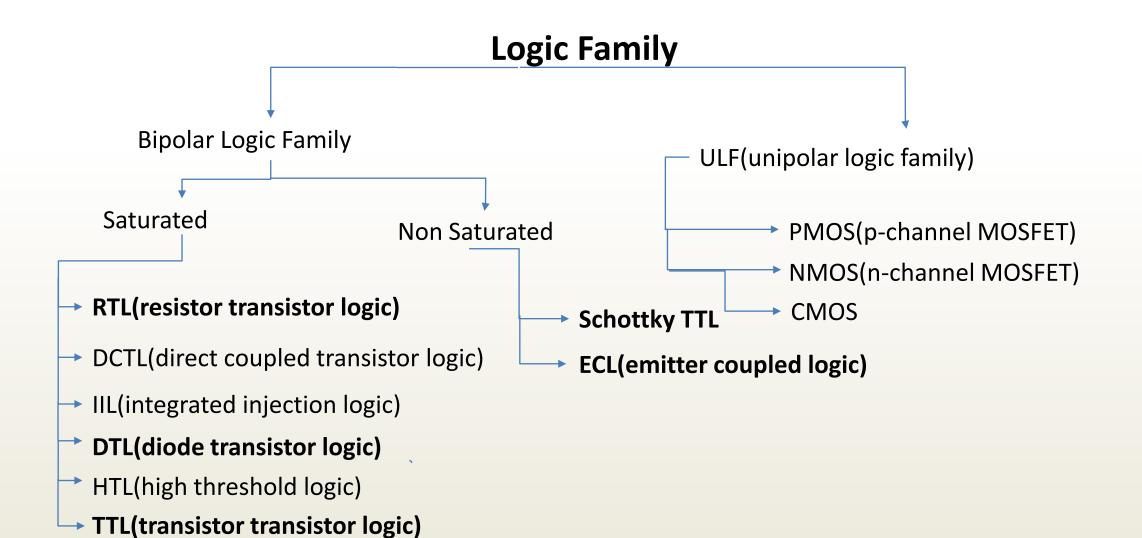

Logic Family Classification

➢ Fan IN And Fan Out

➢Noise Margin

**Transistor as a Switch**

≻RTL, DTL, TTL and ECL

**Elementary data of CMOS**

# Introduction

Logic families represent kind of digital circuit/methodologies for logic expression.

#### **Integration levels :**

| SSI:  | Small scale integration         |

|-------|---------------------------------|

| MSI:  | Medium scale integration        |

| LSI:  | Large scale integration         |

| VLSI: | Very large scale integration    |

| ULSI  | : Ultra large scale integration |

12 gates/chip 100 gates/chip 1K gates/chip 10K gates/chip 100K gates/chip

# Classification

## Fan In

• Fan in or gate is the number of inputs that can practically be supported without degrading practically input voltage level.

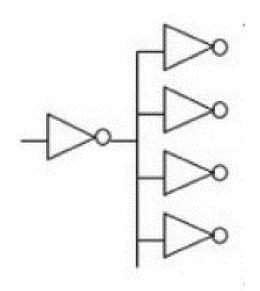

## Fan Out

•The maximum number of digital input that the output of a single logic gate can feed and the gate must be same logic family.

• Fan Out is calculated from the amount of current available in the output of a gate and the amount of current needed in each input of the connecting gate.

•It is specified by manufacturer and is provided in the data sheet.

•Exceeding the specified maximum load may cause a malfunction because the circuit will not be able supply the demanded power.

Fan in = 4

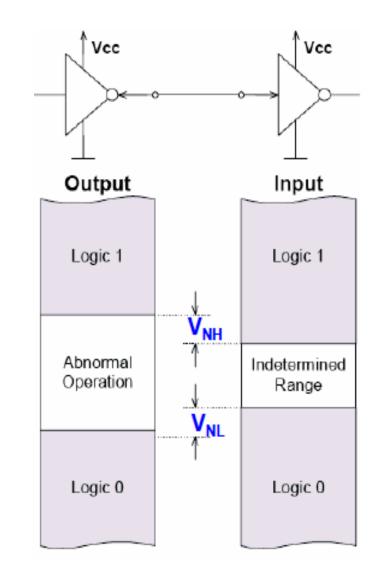

## Noise Margin

•Noise is present in all real systems. This adds random fluctuations to voltages representing logic levels.

•Hence, the voltage ranges defining the logic levels are more tightly constrained at the output of a gate than at the input.

• Small amounts of noise will not affect the circuit. The maximum noise voltage that can be tolerated by a circuit is termed its **noise immunity (noise Margin).**

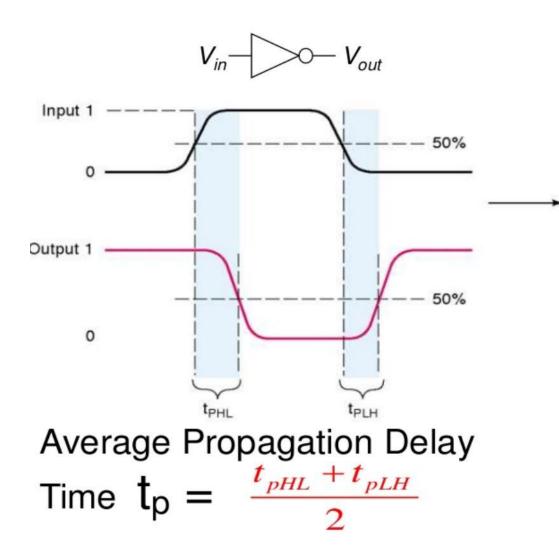

### **Propagation Delay**

A measure of how long it takes for a gate to change state. Ideally, should be as short as possible.

$t_{\text{PHL}}$  - the time it takes the output to go from a high to a low

$t_{\mathsf{PLH}}$  - the time it takes the output to go from a low to a high

# **Basic Characteristics of ICs**

- Propagation delay

- Power dissipation

- Fan in and fan out

- Noise immunity

- Power supply requirement

- Figure of merits i.e. speed power product

- Operating temperature

- · Current and voltage parameters

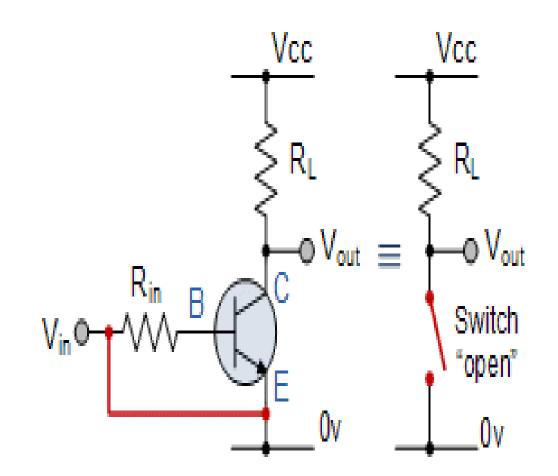

## Transistor as a switch

- A circuit that can turn on/off current in electrical circuit is referred to a switching circuit and transistor can be employed as an electronic switch.

- Cut off region OFF State

Both junctions are reverse biased,

Ic = 0 and V(BE) < 0.7 v</li>

- Saturation region ON State

Ic = maximum and V(BE)>0.7 v

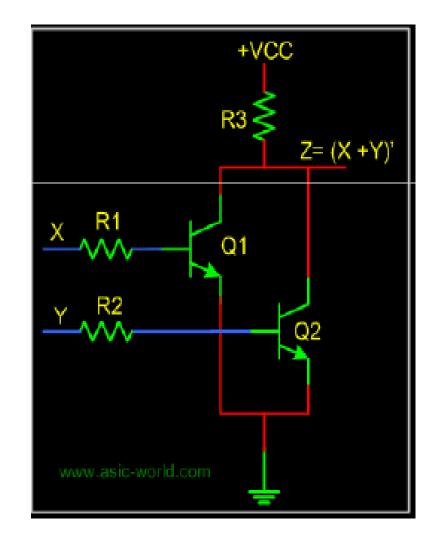

## Resistor Transistor Logic(RTL)

> The basic RTL device is a NOR gate.

> The inputs represent either logic level HIGH (1) or LOW (0).

- The logic level LOW is the voltage that drives corresponding transistor in cut-off region, while logic level HIGH drives it into saturation region.

- If both the inputs are LOW, then both the transistors are in cut-off i.e. they are turned-off. Thus, voltage Vcc appears at output I.e. HIGH.

- If either transistor or both of them are applied HIGH input, the voltage Vcc drops across Rc and output is LOW.

#### Advantages of RTL Logic circuit:

The primary advantage of RTL technology was that it involved a minimum number of transistors, which was an important consideration before integrated circuit technology, as transistors were the most expensive component to produce

#### Limitations:

The obvious disadvantage of RTL is its high current dissipation when the transistor conducts to overdrive the output biasing resistor. This requires that more current be supplied to and heat be removed from RTL circuits. In contrast, TTL circuits minimize both of these requirements:

(NOR GATE USING RTL)

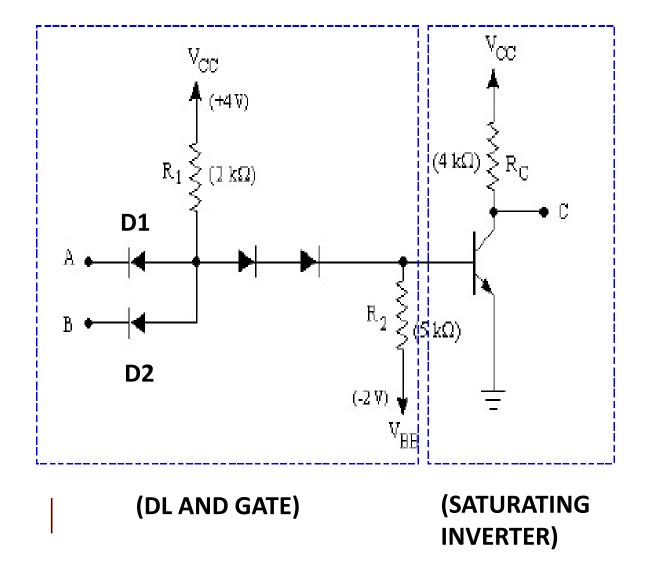

## **Diode Transistor Logic**

- The diode-transistor logic, also termed as DTL, replaced RTL family because of greater fan-out capability and more noise margin.

- > DTL circuits mainly consists of diodes and transistors that comprises DTL devices.

- > The basic DTL device is a NAND gate.

- Two inputs to the gate are applied through diodes viz. D1, D2. The diode will conduct only when corresponding input is LOW.

- If any of the diode is conducting i.e. when at least one input is LOW, the voltage at output keeps transistor T in cut-off and subsequently, output of transistor is HIGH. If all inputs are HIGH, all diodes are non-conducting, transistor T is in saturation, and its output is LOW.

Due to number of diodes used in this circuit, the speed of the circuit is significantly low. Hence this family of logic gates is modified to transistor-transistor logic i.e. TTL family which has been discussed on next slide.

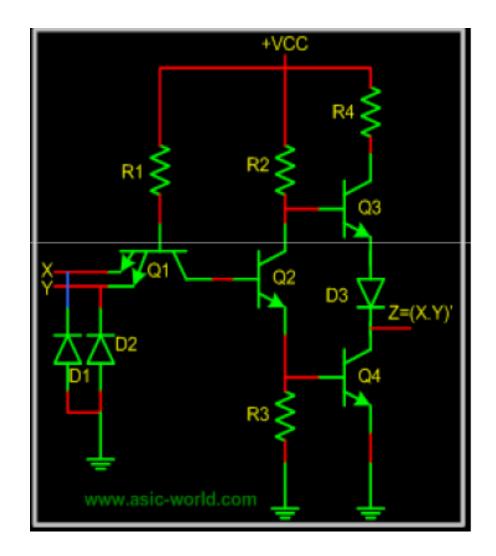

## Transistor Transistor Logic

TTL family is a modification to the DTL. It has come to existence so as to overcome the speed limitations of DTL family. The basic gate of this family is TTL NAND gate.

➢ Q3 is cutoff (act like a high RC) when output transistor Q4 is saturated and Q3 is saturated (act like a low RC) when output transistor Q4 is cutoff. Thus one transistor is ON at one time.

> The combination of Q3 and Q4 is called TOTEM POLE arrangement.

> Q1 is called input transistor, which is multi emitter transistor, that drive transistor Q2 which is used to control Q3 and Q4.

> Diode D1 and D2 are used to protect Q1 from unwanted negative voltages and diode D3 ensures when Q4 is ON, Q3 is OFF.

The output impedance is asymmetrical between the high and low state, making them unsuitable for driving transmission lines. This drawback is usually overcome by buffering the outputs with special line-driver devices where signals need to be sent through cables. ECL, by virtue of its symmetric low-impedance output structure, does not have this drawback.

(BLOCK DIAGRAM OF TTL) <sup>15</sup>

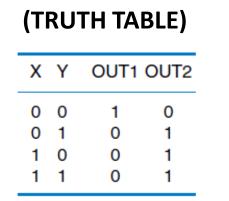

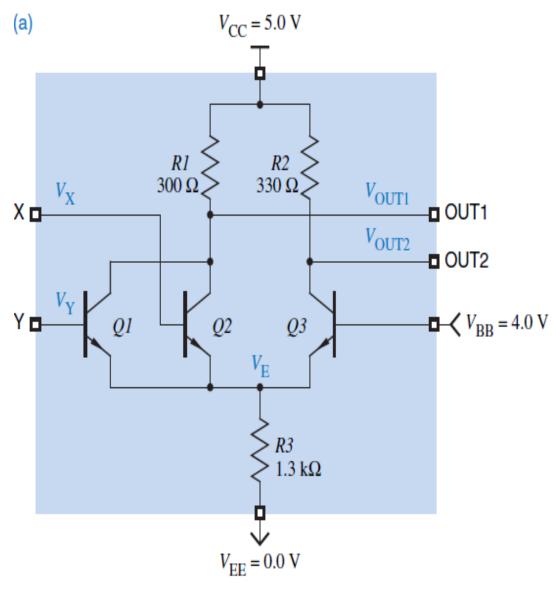

#### **Emitter Coupled Logic**

- ECL logic family implements the gates in differential amplifier configuration in which transistors are never driven in the saturation region thereby improving the speed of circuit to a great extent. The ECL family is fastest of all logic families.

- Based on BJT, but removes problems of delay time by preventing the transistors from saturating.

- > Very fast operation propagation delays of 1ns or less.

- ► Low noise immunity of about 0.2-0.25 V.

- The input impedance is high and the output impedance is low. As a result, the transistors change states quickly, gate delays are low, and the fan out capability is high.

(FUNCTION TABLE)

| Х | Y | $V_{\rm X}$ | $V_{\rm Y}$ | Q1  | Q2  | Q3  | $V_{\rm E}$ | V <sub>OUT1</sub> | $V_{\rm OUT2}$ | OUT1 | OUT2 |

|---|---|-------------|-------------|-----|-----|-----|-------------|-------------------|----------------|------|------|

| L | L | 3.6         | 3.6         | OFF | OFF | on  | 3.4         | 5.0               | 4.2            | Н    | L    |

| L | Н | 3.6         | 4.4         | OFF | on  | OFF | 3.8         | 4.2               | 5.0            | L    | Н    |

| Н | L | 4.4         | 3.6         | on  | OFF | OFF | 3.8         | 4.2               | 5.0            | L    | Н    |

| Н | Η | 4.4         | 4.4         | on  | on  | OFF | 3.8         | 4.2               | 5.0            | L    | Н    |

X

OUT1

OUT2

(ECL 2 INPUT OR/NOR GATE)

### **Complimentary MOS (CMOS)**

- Considerably lower energy consumption than TTL and ECL, which has made portable electronics possible.

- > Most widely used family for large-scale devices

- Combines high speed with low power consumption

- $\succ$  Usually operates from a single supply of 5 15 V

- > Excellent noise immunity of about 30% of supply voltage

- > Can be connected to a large number of gates (about 50).

#### Some statistical characteristics data of different logic families

| S.N. | Parameter                     | DTL   | HTL       | TTL       | RTL    | ECL    | MOS    | CMOS          |

|------|-------------------------------|-------|-----------|-----------|--------|--------|--------|---------------|

| 1.   | Basic Gates (Positive Logic)  | NAND  | NAND      | NAND      | NOR    | OR-    | NAND   | NOR or        |

|      |                               |       |           |           |        | NOR    |        | NAND          |

| 2.   | Fan out (Minimum)             | 8     | 10        | 10        | 5      | 24     | 20     | >50           |

| 3.   | Typical power dissipation per | 8-12  | 55        | 12-22     | 12     | 40-55  | 0.2-10 | 0.01 static 1 |

|      | gate, mW                      |       |           |           |        |        |        | at 3 MHz      |

| 4.   | Noise immunity                | Good  | Excellent | Very good | Medium | Good   | Medium | Very good     |

| 5.   | Typical propagation           | 30    | 90        | 12-6      | 12     | 4-1    | 300    | 70            |

|      | delay/gate, ns                |       |           |           |        |        |        |               |

| 6.   | Clock rate (minimum           | 12-30 | 4         | 15-60     | 8      | 60-400 | 2      | 5             |

|      | frequency at which flip-flops |       |           |           |        |        |        |               |

|      | operate), MHZ                 |       |           |           |        |        |        |               |

| 7.   | Number of functions           | Fairy | Medium    | Very high | high   | High   | Low    | Low           |

|      |                               | High  |           |           |        |        |        |               |

## References

✓ Switching Circuit and Logic Design by Prof. Indranil Sengupta, IIT KGP

- ✓ Modern digital Electronics by R P Jain

- ✓ NPTEL VIDEO by Dr. Amitava Dasgupta, IITM

- ✓ Logic Families by Dr. Basem Elhalawany

- ✓ Logic Gates and Family by Dr. A. P. VAJPEYI, IITG